## **3. Introduction to the Nexys 4 FPGA Board:**

Please review Nexys 4 details from your first week of lab/lecture material dir pdf pdf .avi .

## 4. FPGA Design Flow:

Please refer to your first week's lab on Nexys 4: Xilinx\_project\_synthesis\_on\_Vivado .pdf .mp4

5. Prelab: (Refer to the first paragraph of <u>nexys4\_rm.pdf</u> for the first two questions)

Q 5. 1: Circle the family and device category of the FPGA used on Nexys4 board? (1pt)

| 7 Series  |          | UltraScale                          |   | UltraScale+        |                    |

|-----------|----------|-------------------------------------|---|--------------------|--------------------|

| Spartan-7 | Artix-7  | Kintex UltraScale Virtex UltraScale |   | Kintex UltraScale+ | Virtex UltraScale+ |

| Kintex-7  | Virtex-7 | ''                                  | - |                    |                    |

Q 5. 2: Google "CSG324 @Xilin.com" and find what is CSG324 in the part number of the device used on Nexys-4? (1pt)

□ Speed grade □ Package □ Serial number □ Model number

- Q 5. 3: The **state memory** is usually implemented using: (2pts)

- □ And-Or gates

- □ RAM

- □ flip-flops

- □ latches

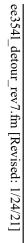

- Q 5. 4: We will implement the detour signal controller using One-Hot state assignment method. How many D-flip-flops are needed to implement the controller? (2pts)

On power-on reset (i.e when power is first applied to the system), how many Flip-Flops are preset? \_\_\_\_\_\_ (1pt) and how many are cleared? \_\_\_\_\_\_ (1pt)

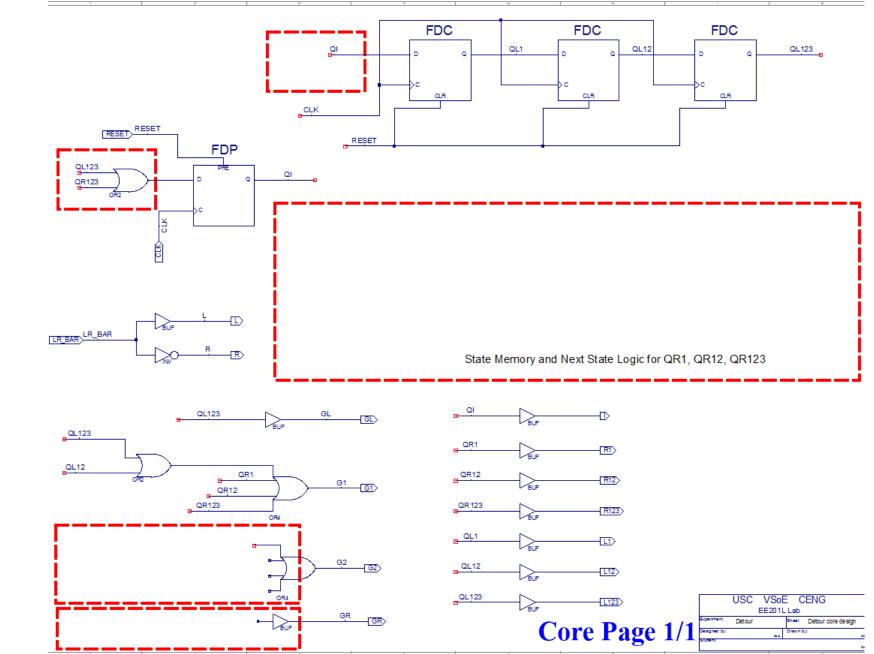

In the schematic ee2541\_detour.sch (on page 11), next state logic for which state(s) is complete? (2pts)

Next State Logic (NSL) is purely a \_\_\_\_\_\_(*combinational/sequential*) circuit. (2pts)

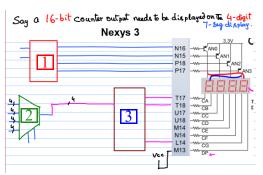

Q 5. 5: Refer to the figure on the right, reproduced from this <u>pdf</u>, suggesting a way to display the output of a 16-bit binary number as a 4-digit hexadecimal number going from 0000 to FFFF on the 4 SSDs of a Nexys-3 board.

Name the three components and also state whether it is a combinational logic or a sequential logic.

- 1.\_\_\_\_\_

- 2.\_\_\_\_\_3.

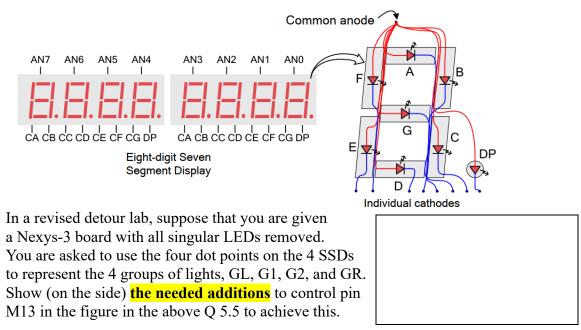

Now, if we want to display the output of a 32-bit binary counter as an 8-digit hexadecimal number going from 0000 0000 to FFFF FFFF on the 8 SSDs of a Nexys-4 board, what three components you intend to use?

Do you believe that one of the above two displays is brighter. \_\_\_\_\_ Yes / No. If you said "Yes", then which is brighter? \_\_\_\_\_ (A/B). A= 16-bit counter display on the 4 digits of Nexys-3, B= 32-bit counter display on the 8 digits of Nexys-4 Why?

- Q 5. 6: In the above diagram, VCC (= 3.3 volts = a constant logic 1) was tied inside the FPGA to the DP (via pin M13) to make \_\_\_\_\_ (one dot point/all dot points) continuously \_\_\_\_\_ (to be on/to be off).

- Q 5. 7: Though we do not perform fractional arithmetic needing to display a dot point (such as the dot point in 23.42 or 1.234) in this course, it is possible to do so as the so called SSDs (Seven Segment Displays) contain actually 8 segments per digit including the dot point.

## 7. Lab Report:

Name:

Date:

Lab Session:

TA's Signature:

| <b>For TAs:</b> Pre-lab (10): | Schematic completion (70): | Report (out of 20): |

|-------------------------------|----------------------------|---------------------|

| Comments:                     |                            |                     |

- Q 7. 1: Refer to Xilinx UG616. What are the two different D-flip-flops that are used in this lab? What is the difference between them? (2pts)

- Q 7. 2: Name 2 more D-flip-flops that are available in the Xilinx library UG616 (and have enable pins) and briefly explain how are they different from the ones that are used in this lab.(8pts)

- Q 7. 3: Which pin of the FPGA is connected to the **BtnC** on the Nexys 4 board? Refer to the reference manual for the Nexys 4 or the .xdc file of Nexys 4 (see files in the dir). (4pts)

Q 7. 4: Which three special buffers are needed for signals that connect to the input and output devices (including the on-board clock generator)? Give their names and whether they are needed to connect inputs or outputs or both. (6pts)

Q 7. 5: The frequency of the clock entering the FPGA is 100MHz. Notice that we are dividing the input clock by using counters. Calculate the frequency of the divided clock (DIVCLK[25]) that triggers the detour signal state machine. (5pts)

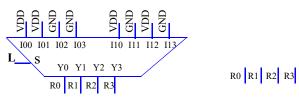

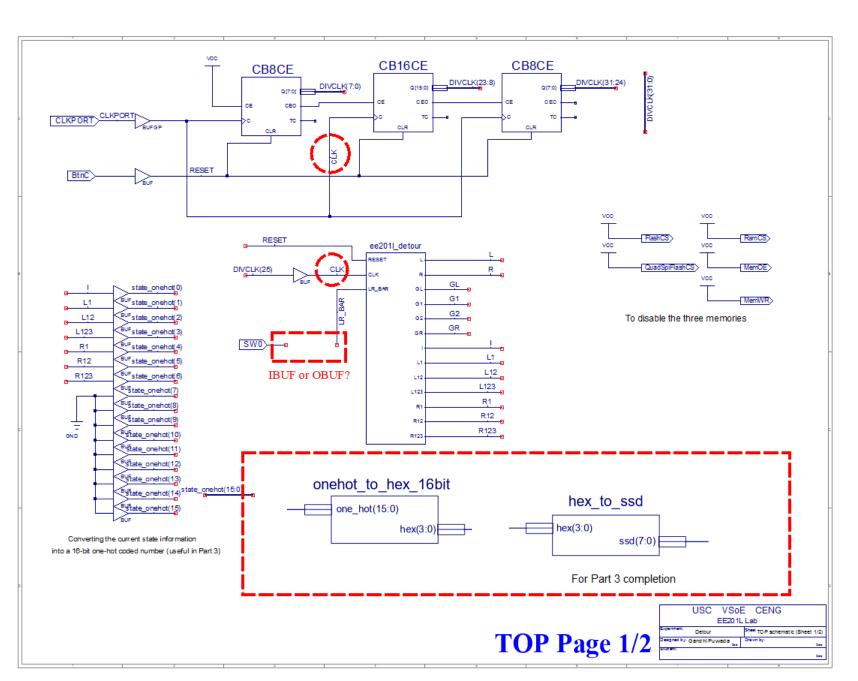

Q 7. 6: Here, L (for Left) and R (for Right)

5 pts are always opposite to each other. Can you optimize (simplify) the 4bit output R0 R1 R2 R3 generating combinational logic on the side? Try to avoid the expensive 4-bit wide 2-

to-1 mux by tying either VDD or GND or L or R

as appropriate to each of the four outputs.Note: Since R = -L, instead of generating L\_Bar by inverting L, you can use R wherever you need L\_Bar.

Based on the above, you suggest that you could have avoided \_\_\_\_\_

in the second page of the top schematic.

ee3541\_detour\_rev7.fm [Revised: 1/24/21]

Detour Signal Lab

## Part 3 On this page generate only Anode and Cathode controls.

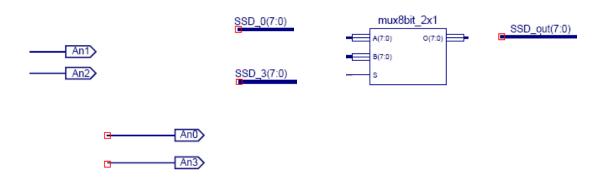

Method #1: Permanently disable AN1 and AN2. Then activate AN0 and AN3 alternately at a reasonable speed *(neither too fast nor too slow,* your TA will help) while sending the correct 7-segment (actually 8-segment) signals (Ca-Cg) to the SSDs. You need a 8-bit wide 2-to-1 mux for this. You might use DIV-CLK (15) to alternately enable one of SSD0 or SSD3 to accomplish this.

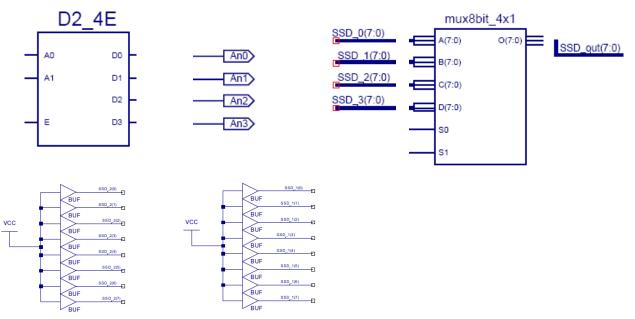

Method #2: Instead of permanently disabling AN1 and AN2 (as in Method#1), let us send Ca-Cg, Dp=11111111 to the 8 cathodes (remember these are active low so this will blank the displays). Now we need to activate the 4 anodes, one at a time in sequence, while sending the corresponding 8-segment information to the cathodes with a 8-bit wide 4-to-1 mux. You can use perhaps DIVCLK(15:14) for this purpose.

You can use a 2x4 decoder such as the above  $D2_4E$ . Look up the Xilinx library UG616 for the D2\_4E decoder to check if the enable input is active high or low and the outputs are active high or active low. We also provided you with the 8-bit wide 4x1 mux shown above. The diagrams on pages 18/29 to 20/29 (section 9.1 on Seven Segment Display) of the Nexys 4 reference manual will help you in understanding the scanning operation. Celebrate the completion of your lab!